پنجشنبه ۱۸ مرداد ۹۷

دارپا، تیم تحقیقاتی دو پروژهی جدید خود را برای عبور از قوانین مور و طراحی تراشههایی سریعتر و با مصرف انرژی کمتر مشخص کرد.در ادامه همراه با عبیاتی باشید.

آژانس پروژههای تحقیقاتی پیشرفته دفاعی آمریکا (DARPA) در تلاش است تا از مرز قوانین تعریفشدهی مور عبور کرده و کامپیوترهایی ۱۰۰۰ برابر سریعتر و در عین حال با مصرف انرژی کمتری را توسعه دهد. دارپا برای پیشبرد پروژههای تحقیقاتی جدید خود، تیمهای تخصصی مربوطه به هر پروژه را مشخص کرد تا اهداف دارپا را دنبال کنند.

پروژههای جدید دارپا تحت عنوان برنامهی 3DSoC و برنامهی FRANC، بخشی از پروژهی بزرگ ۱.۵ میلیار دلاری ERI است که نوآوریهای جدید در صنعت الکترونیک را موردبررسی قرار میدهند. برنامههای 3DSoC و FRANC تولید تراشههای قویتر با قدرت محاسباتی بالاتر و کارآمدتر را در برنامهی خود قرار دادهاند. دارپا، هر دو پروژه را در ماه سپتامبر معرفی کرد.

دارپا هفتهی گذشته، در اولین نشست برنامهی ERI در سان فرانسیسکو، تیمهای تحقیقاتی که قرار است روی پروژههای جدید کار کنند را رسما مشخص کرد. برای پروژهی 3DSoC، گروههای تحقیقاتی از موسسهی فناوری گرجستان، دانشگاه استنفورد، موسسه تکنولوژی ماساچوست و موسسهی تکنولوژی Skywater وارد موضوع شدهاند. بهمنظور بهنتیجه رسیدن پروژهی FRANC نیز آزمایشگاه HRL، شرکت Applied Materials، شرکت Ferric، دانشگاه کالیفرنیا در لسآنجلس؛ دانشگاه مینهسوتا و دانشگاه ایلینوی در Urbana-Champaign وارد همکاری در این پروژه شدهاند. دارپا در پروژهی 3DSoC هدف مشخصی را دنبال میکند که آن را بهصورت مشخص تعریف کرده است: «توسعهی مواد، ابزارهای طراحی و تکنیکهای ساخت در تولید میکروسیستمها روی بستر مجزا در مدارهای مجتمع سهبعدی».

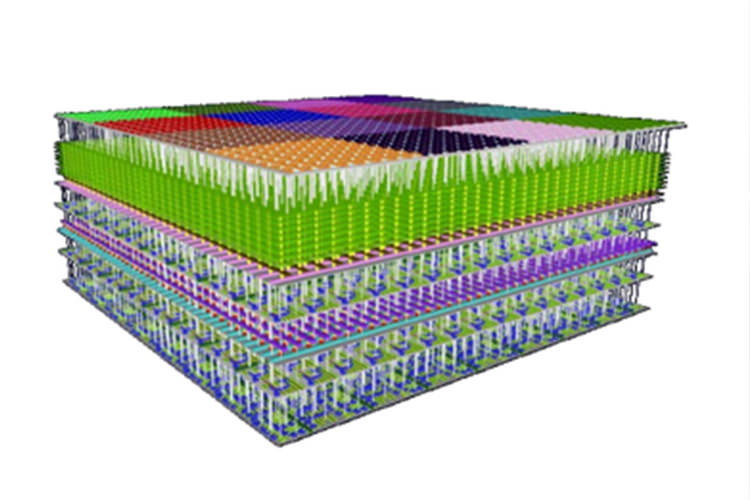

در واقع، ایدهی اصلی این پروژه، تولید مدارهای مجتمع عمودی یکپارچه است که هم شامل بخش حافظه و هم بخش محاسبات منطقی و البته ورودی و خروجی تراشه میشود. مزیت طراحی سهبعدی آن است که زمان انتقال دادهها بین اجزای مختلف بهطرز چشمگیری کاهش مییابد و در کل، فرآیند نهایی باسرعت بیشتر و کارایی بهتری عمل خواهد کرد.

لینتون سلمون، مدیر بخش 3DSoC دفتر فناوریهای میکروسیستم معتقد است:

در پروژهی 3DSoC، محققان، یک دهه تلاش و کوشش ارزشمند تئوری و مطالعات تحقیقاتی دانشگاهی را تجمیع میکنند تا فرآیند تولید مدار مجتمع را تغییر دهند و در عمل، از فناوریهای مربوط به حوزههای میکروالکترونیک استفاده کنند.

دارپا معتقد است تراشههای سهبعدی 3DSoC در مقایسه با تراشههای معمولی که بهنام تراشههای 2D گسسته شناخته میشوند، زمان محاسبات را در بیش از ۵۰ لایه کاهش میدهند. این کاهش سرعت زمان محاسبات در حالی است که مقدار انرژی مصرفشده تراشههای جدید بهمراتب کمتر از تراشههای فعلی خواهد بود. برای محقق ساختن این اهداف، طراحی 3DSoC باید بتواند از پهنای باند اتصال بین لایههای ۵۰ ترابیت در ثانیه پشتیبانی کند؛ که البته نیازی به حافظهی بیش از ۲ پیکوژول در هر بیت ندارد.

یکی از اهداف اصلی پروژهی 3DSoC، حل محدودیتهای مربوط به پهنای باند، زمان تاخیر و مصرف انرژی در معماری تراشههای فعلی است. البته این محدودیتها تا حدودی در تراشههای 3D و 2.5D پردازندههای انویدیا تسلا و پردازندهی گرافیکی AMD رادئون و همچنین در پردازندههای Xeon Phi برطرف شدهاند؛ ولی طراحی تراشهی پروژهی 3DSoC، کمی پیچیدهتر از روشهای فعلی است و شامل دوازده یا تعداد بیشتری لایه برای یکپارچهسازی قسمتهایی همچون حافظهی رم مقاومتی ReRAM، ترانزیستورهای CNFET و هستههای پردازندههای مبتنی بر سیلیکون MOSFET میشود.

محققان دانشگاه استنفورد نیز قبلا چنین شبیهسازی 3D را روی طراحی معماری ۷ نانومتری و فرآیند ۹۰ نانومتری شبیهسازی کردهاند و این مدلها را به مدلهای آموزشی و استنتاجی شبکههای عصبی اعمال کردهاند. شبیهسازی انجامشده، مزایای قابلتوجهی را در فرآیند کلی نشان داد. زمان انجام محاسبات در تراشههای جدید هم نسبت به تراشههای 2D معمولی با معماری ۷ نانومتری، بسیار کاهش یافت و انرژی کمتری هم مصرف شد. محققان اعلام کردند که تراشه با معماری ۷ نانومتری سهبعدی نسبت به تراشهی ۲ بعدی، مزایای ۶۴۶ برابری را در مقایسه با ۳۲۳ برابری تراشهی دوبعدی نشان میدهد. حتی در طراحی معماری ۹۰ نانومتری نیز، 3D SoC شبیهسازیشده، مزایای ۳۵ تا ۷۵ برابری را نسبت به تراشههای دوبعدی معمولی نشان میدهد. نتایج مشابهی در الگوریتمهای مختلفی از جمله رگرسیون خطی، رگرسیون لجستیک، PageRank، SSSP و BFS نیز مشاهده شد.

پروژهی FRANC یکی دیگر از برنامههای دارپا، ارتباط مستقیمی با پروژهی 3DSoC دارد. این پروژه، بهطور انحصاری به بررسی حافظهی منطقی یا لاجیم تراشه میپردازد. هدف برنامهی FRANC، تفکیک و جداسازی عملکرد حافظهی منطقی و حافظهی معمولی در معماری شناختهشدهی von Neumann است. ایدهی اصلی این پروژه، انجام محاسبات روی دادهها در همان محل ذخیرهسازی است. یعنی برای پردازش دادهها، دیگر نیازی به انتقال آنها با فضای دیگری وجود ندارد و در همان محل پردازش دادهها انجام میشود. چنین طراحی سرعت محاسبات را بهشدت بالا میبرد و علاوهبر بالا بردن میزان کارایی، در مصرف انرژی هم صرفهجویی میشود. برای محقق ساختن این برنامه، نیاز به طراحی جدید، مواد جدید و تکنیکهای جدیدی است که محققان باید آن را عملی کنند.

ییکی چن، مدیریت پروژهی FRANC را برعهده دارد. پروژهی FRANC فعالیتهایی را در حوزهی پردازش دادهها در حافظه و پردازش دادهها در حافظه دنبال میکند و با اینکه شباهتهایی به پروژهی STARnet دارپا دارد؛ ولی مسیر خودش را میرود. بهطور خاص، این پروژهی جدید دارپا قصد دارد با استفاده از مواد و فناوریهای جدید یکپارچهسازی، به مدیریت انرژی در تراشههای CMOS و DRAM بپردازد و در تولید حافظههایی با فناوریهای نوین عملکردی متفاوت داشته باشد.

هر دو برنامهی جدید دارپا یعنی 3DSoC و FRANC امید طراحی تراشههایی با سرعت بالا و مصرف انرژی کمتر را میدهند. دراپا در برنامهریزی خود، پروژهی 3DSoC را برای بازهی زمانی ۴.۵ ساله طراحی کرده است؛ در حالی که پروژهی FRANC باید ظرف مدت ۳.۵ سال به نتیجه برسد. با توجه به اینکه تیمهای تحقیقاتی پروژهها تعیین شدهاند، انتظار میرود کار جدی بهزودی استارت بخورد.